#### Microprocessor I/O

# (Chapter 5)

# Microprocessor I/O

- Data Communication,

- Parallel I/O

- Serial communication

- Serial interface and UART modems

- I/O devices, D/A, A/D interface, special I/O devices.

# Tx and Rx

- The UART has a transmission-engine, and also a reception-engine, which are able to operate simultaneously (i.e., "full-duplex")

- Software controls the UART's operations by accessing several registers, using the x86 processor's 'in' and 'out' instructions

- Linux provides some convenient 'macros' that 'hide' the x86 machine-code details

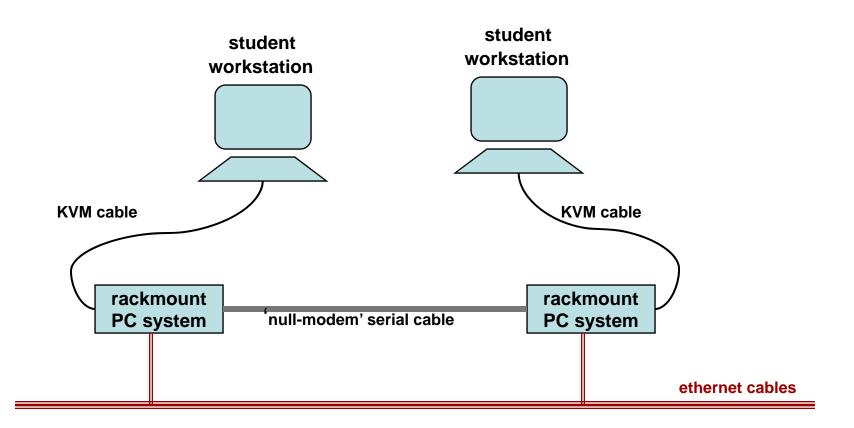

## PC-to-PC communications

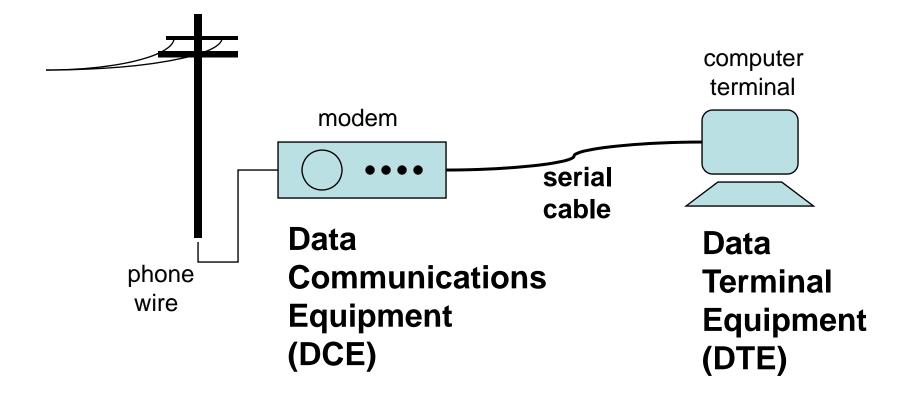

# DCE and DTE

- Original purpose of the UART was for PCs to communicate via the telephone network

- Telephones were for voice communication (analog signals) whereas computers need so exchange discrete data (digital signals)

- Special 'communication equipment' was needed for doing the signal conversions (i.e. a modulator/demodulator, or modem)

#### PC with a modem

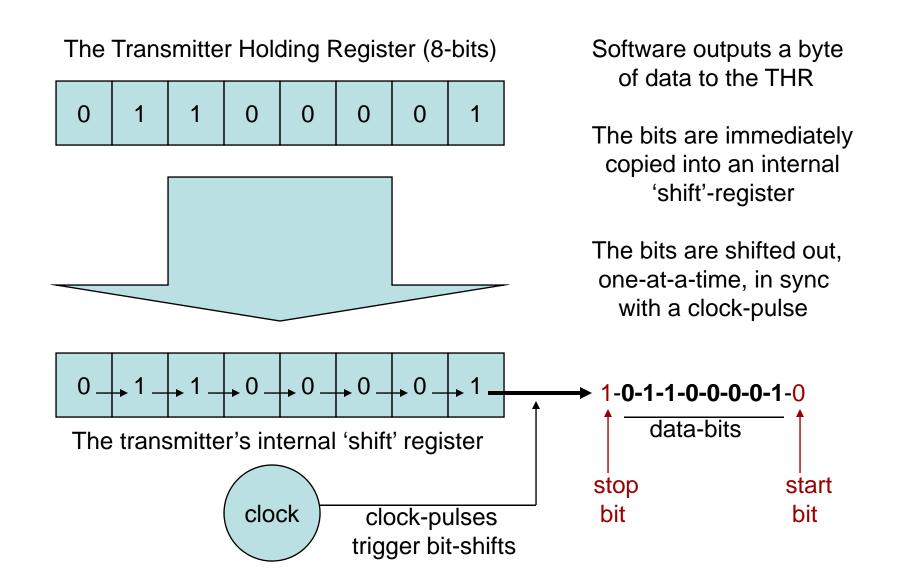

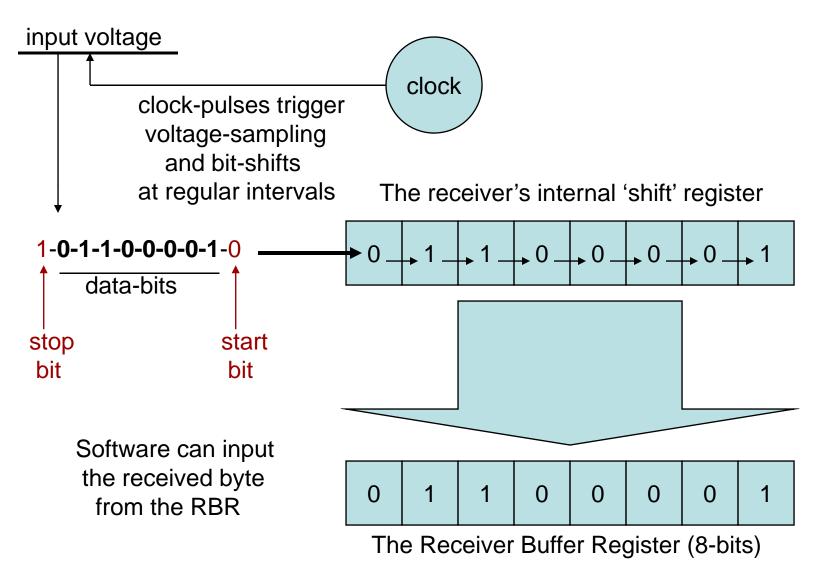

## Serial data-transmission

#### Serial data reception

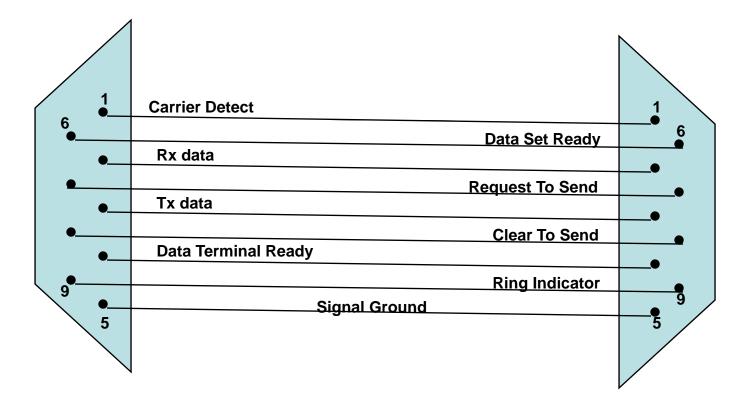

#### Normal 9-wire serial cable

# Signal functions

- CD: **Carrier Detect** The modem asserts this signal to indicate that it successfully made its connection to a remote device

- RI: **Ring Indicator** The modem asserts this signal to indicate that the phone is ringing at the other end of its connection

- DSR: Data Set Ready Modem to PC

- DTR: Data Terminal Ready PC to Modem

# Signal functions (continued)

- RTS: **Request To Send** PC is ready for the modem to relay some received data

- CLS: Clear To Send Modem is ready for the PC to begin transmitting some data

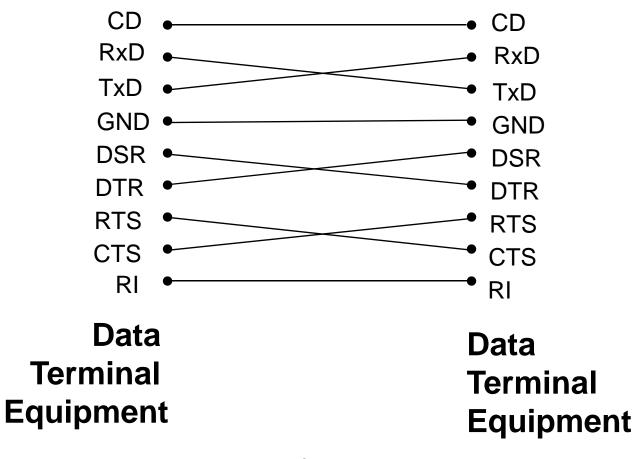

#### 9-wire null-modem cable

no modems

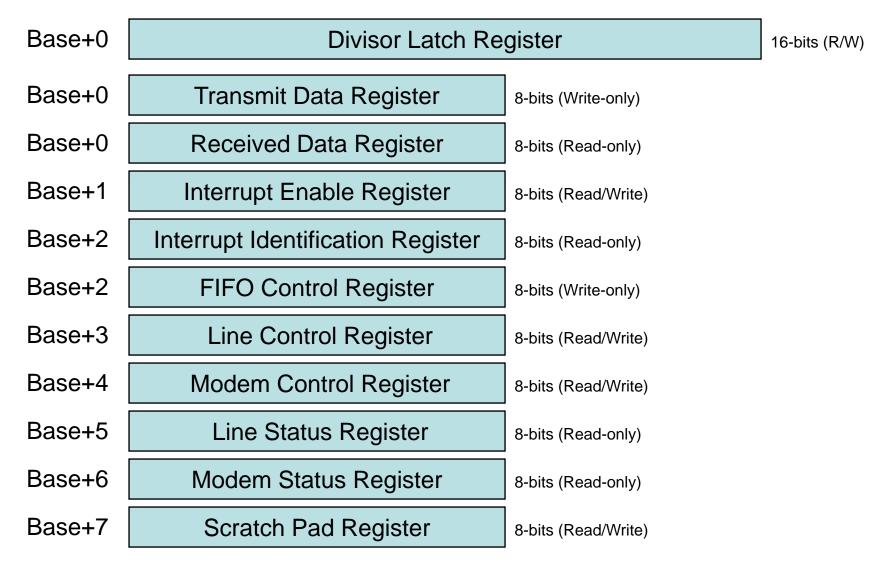

# The 16550 UART registers

#### Rate of data-transfer

- The standard UART clock-frequency for PCs equals 1,843,200 cycles-per-second

- Each data-bit consumes 16 clock-cycles

- So the fastest serial bit-rate in PCs would be 1843200/16 = 115200 bits-per-second

- With one 'start' bit and one 'stop' bit, ten bits are required for each 'byte' of data

- Rate is too fast for 'teletype' terminals

## **Divisor Latch**

- The 'Divisor Latch' may be used to slow down the UART's rate of data-transfer

- Clock-frequency gets divided by the value programmed in the 'Divisor Latch' register

- Older terminals often were operated at a 'baud rate' of 300 bits-per-second (which translates into 30 characters-per-second)

- So Divisor-Latch was set to 0x0180

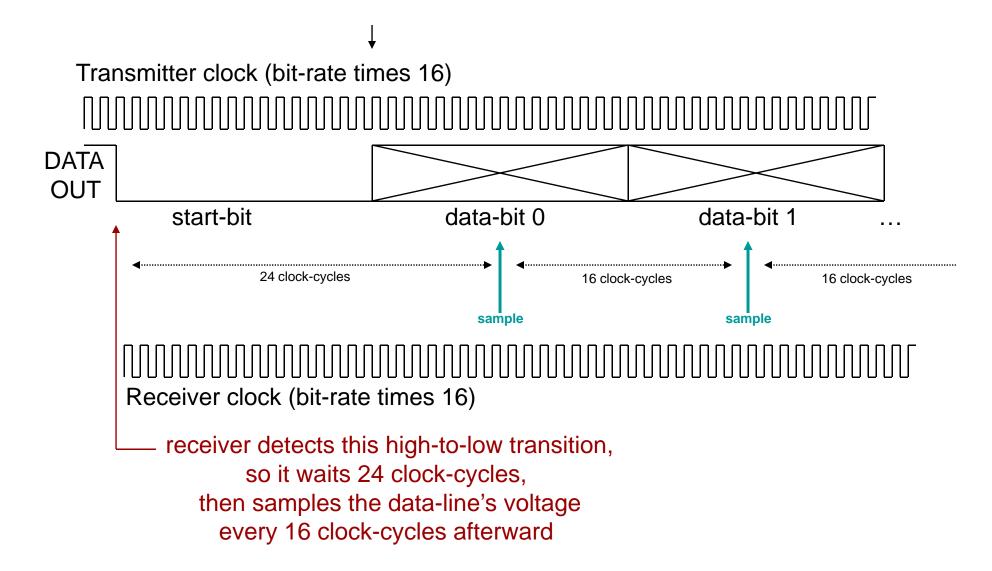

# How timing works

# Programming interface

The PC uses eight consecutive I/O-ports to access the UART's registers

|         | 0x03F8                                                                                                                                                                     | 0x03F9 | 0x03FA  | 0x03FB                      | 0x03FC                       | 0s03FD | 0x03FE                           | 0x03FF |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|-----------------------------|------------------------------|--------|----------------------------------|--------|

|         | RxD/TxI                                                                                                                                                                    | D IER  | IIR/FCR | LCR                         | MCR                          | LSR    | MSR                              | SCR    |

| transmi | RxD/TxD IER IIR/   interrupt interrupt   enable register   eceive buffer register and ransmitter holding register   ansmitter holding register iso Divisor Latch register) |        | er      | line<br>control<br>register | modem<br>control<br>register |        | modem<br>status<br>register<br>s |        |

interrupt identification register and FIFO control register

## Modem Control Register

| 7 | 6 | 5 | 4            | 3    | 2    | 1   | 0   |

|---|---|---|--------------|------|------|-----|-----|

| 0 | 0 | 0 | LOOP<br>BACK | OUT2 | OUT1 | RTS | DTR |

Legend:

DTR = Data Terminal Ready (1=yes, 0=no) RTS = Request To Send (1=yes, 0=no) OUT1 = not used (except in loopback mode) OUT2 = enables the UART to issue interrupts LOOPBACK-mode (1=enabled, 0=disabled)

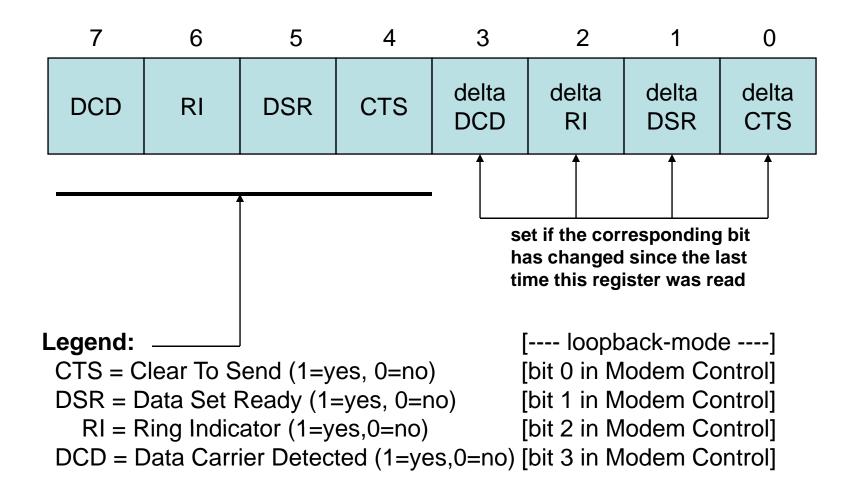

## Modem Status Register

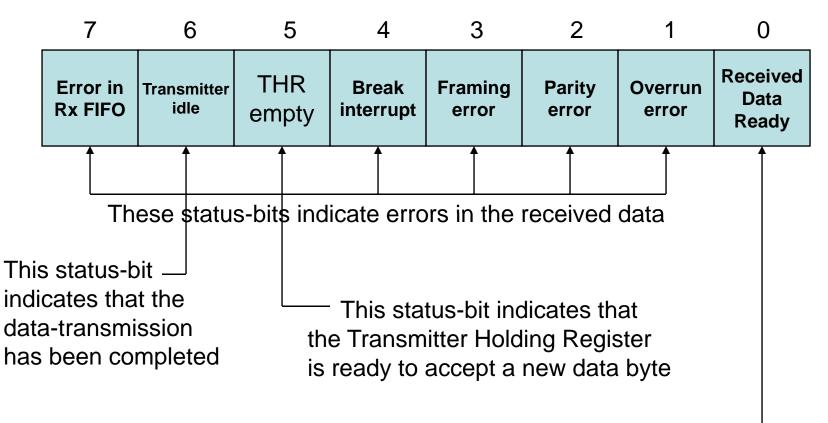

## Line Status Register

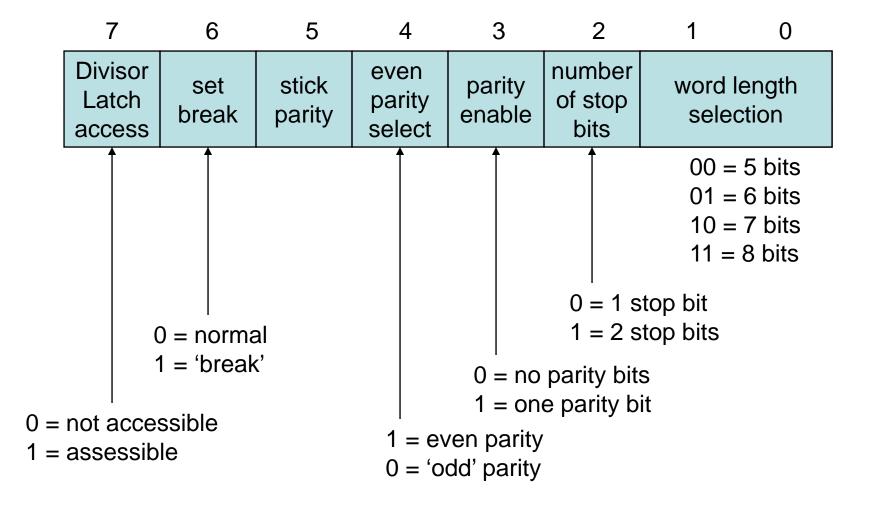

## Line Control Register

## Interrupt Enable Register

|                                                                                                                               | 7 | 6 | 5 | 4 | 3                         | 2                           | 1                  | 0                                |

|-------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---------------------------|-----------------------------|--------------------|----------------------------------|

|                                                                                                                               | 0 | 0 | 0 | 0 | Modem<br>Status<br>change | Rx Line<br>Status<br>change | THR<br>is<br>empty | Received<br>data is<br>available |

| If <b>enabled</b> (by setting the bit to 1),<br>the UART will generate an interrupt:<br>(bit 3) whenever modem status changes |   |   |   |   |                           |                             |                    |                                  |

Also, in FIFO mode, a 'timeout' interrupt will be generated if neither FIFO has been 'serviced' for at least four character-clock times

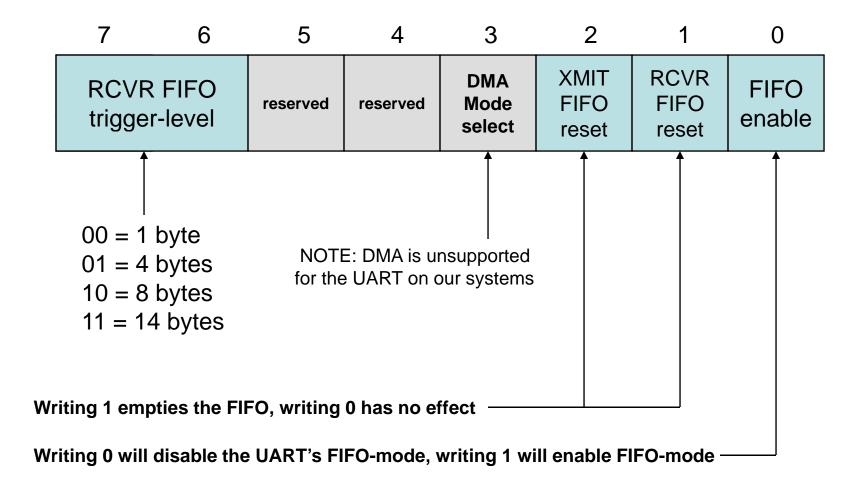

# **FIFO Control Register**

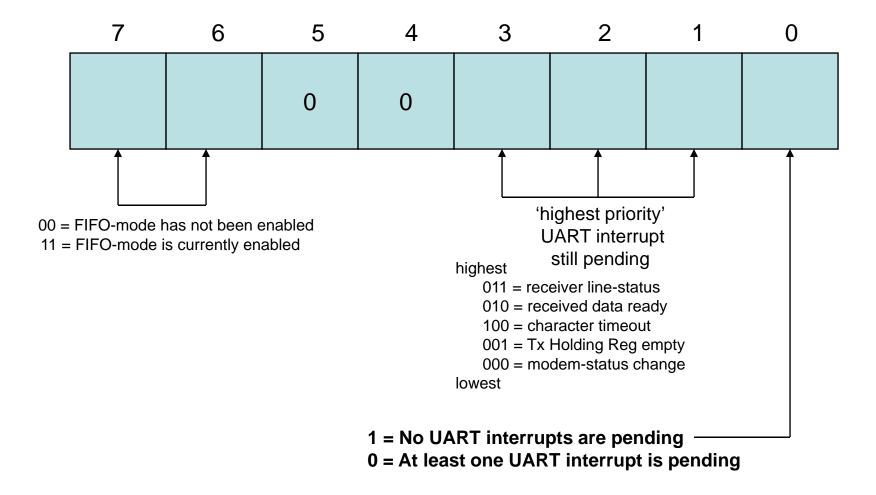

## Interrupt Identification Register